La puce a été conçue par T-Head, une jeune unité de semi-conducteurs fonctionnant sous la responsabilité fr l'Académie DAMO d'Alibaba. Yu Pu, responsable des produits de pointe pour T-Head, a parlé de la puce lors de l'événement Hot Chips 2020, affirmant qu'Alibaba se tournait vers RISC-V comme base de son infrastructure de cloud computing et de pointe. Pu a admis que c'était au début du développement de l'architecture, mais que les ingénieurs de l'entreprise avaient confiance en la technologie et en la manière dont ils pouvaient travailler avec la communauté open source pour l'améliorer.

«Bien que le RISC-V ne soit pas encore assez mature en termes de technologie et d'écosystème, nous pensons qu'il a un grand potentiel», a-t-il déclaré. «L'intention de ce travail est de contribuer aux cœurs de calcul embarqués haut de gamme et hautes performances basés sur RISC-V grâce à une collaboration open source.»

«RISC-V est très attractif en ce moment car en tant qu'alternative aux ISA fermés et coûteuses, l'ISA RISC-V ouverte et gratuite accélère l'innovation des processeurs grâce à une collaboration à standard ouvert», a déclaré Pu. «L'évolutivité, l'extensibilité et la modularité permettent aux clients de processeurs… d'optimiser pour les charges de travail spécifiques au domaine, telles que les accélérateurs de machines, le traitement réseau, les dépenses de sécurité, les contrôleurs de stockage, etc., améliorant ainsi largement l'efficacité du traitement et réduisant les coûts de conception. RISC-V est également très facile à accompagner avec d'autres IP spécifiques aux domaines des partenaires, à la fois du point de vue technique et commercial. RISC-V est en train de devenir un peu comme… le système d'exploitation Unix et Unix. Il est également entièrement pris en charge par notre AliOS [distribution Linux d'Alibaba]. Au fur et à mesure que la chaîne d'outils devient de plus en plus mature, elle améliore encore l'expérience logicielle et réduit les coûts de développement logiciel. »

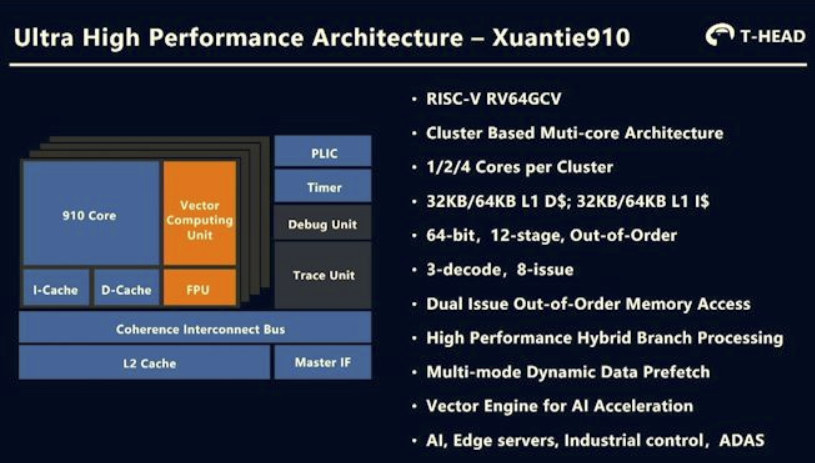

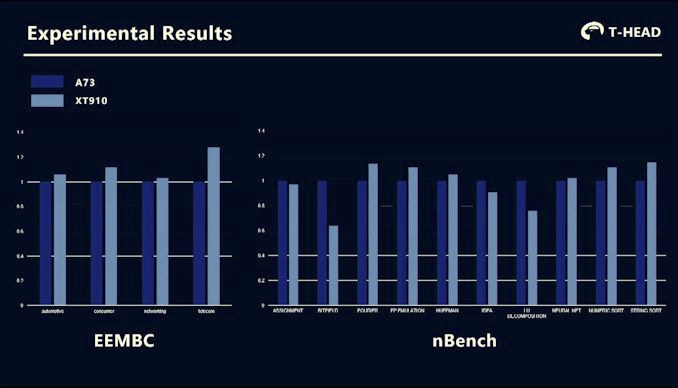

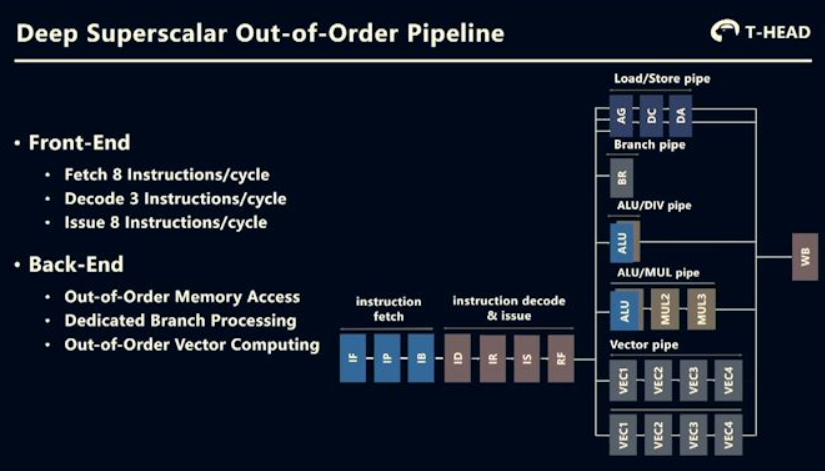

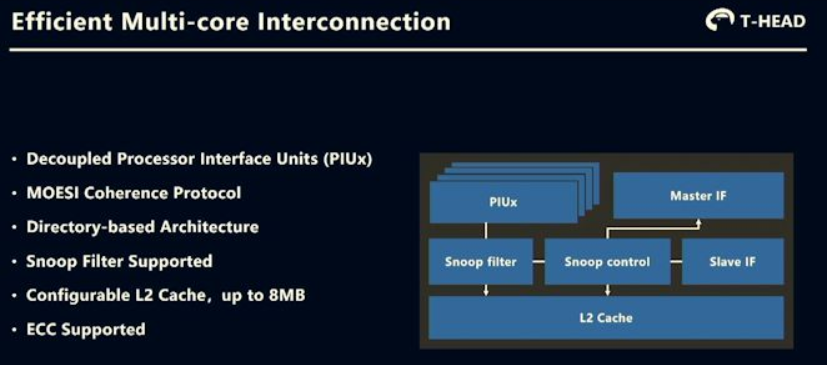

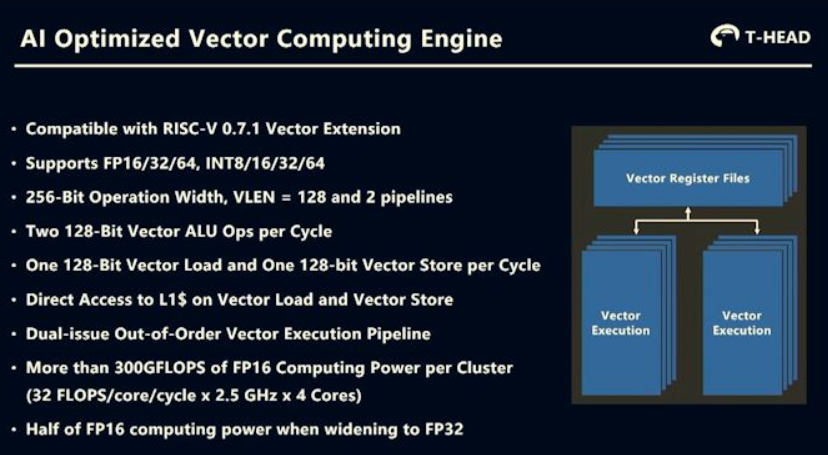

Le XT910 prend en charge RISC-V 0.7.1 Vector Extension, comprend un moteur vectoriel pour l'accélération de l'IA et est basé sur des processus FinFET 12 nanomètres de Taiwan Semiconductor Manufacturing Corp.Il s'agit d'une conception multicœur basée sur un cluster avec jusqu'à quatre cœurs par cluster et chaque cœur prend en charge 32 Ko à 64 Ko de cache de données L1 et 32 Ko à 64 Ko de cache d'instructions L1. Il comprend un prédicteur de branche hybride, mettant en œuvre plus d'un mécanisme de prédicteur pour améliorer les performances et l'efficacité. La puce offre également la fonction RISC-V Turbo qui utilise des modifications telles que la synchronisation de plusieurs cœurs et un accès mémoire plus rapide pour augmenter les performances, mais elle peut également être désactivée pour permettre à la puce d'être complètement compatible avec d'autres puces RISC-V.

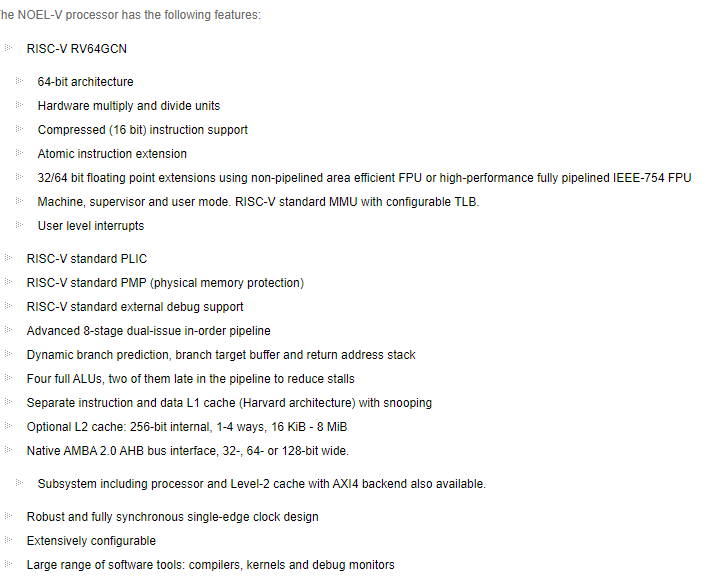

Caractéritiques du processeur RISC-V XT910

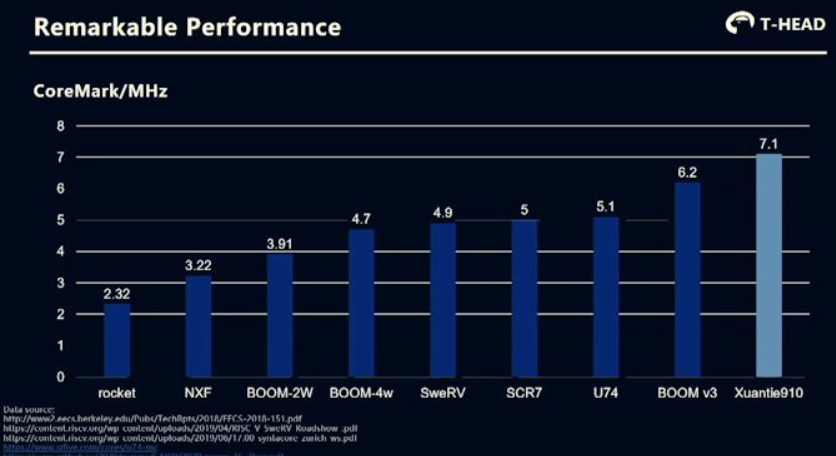

- Processeur - Jusqu'à 16 cœurs RISC-V (RV64GCV) 64 bits avec extension RISC-V Vector et extension Turbo personnalisée en quatre clusters de quatre cœurs; 12 étages ; Marque: 7,1 par MHz

- Cache - 32 Ko ou 64 Ko de cache I / D par cœur, jusqu'à 8 Mo de cache L2 par cluster

- Unité à virgule flottante FP16-FP64

- Unité de calcul vectoriel (aka Vector Engine) pour l'accélération de l'IA

- Gestion de la mémoire - Sv39 MMU + 8/16 PMP

- Contrôleur d'interruption - Clint + PLIC

- Processus - Final: FinFET 12 nm; échantillons d'ingénierie: TSMC 28nm HPC

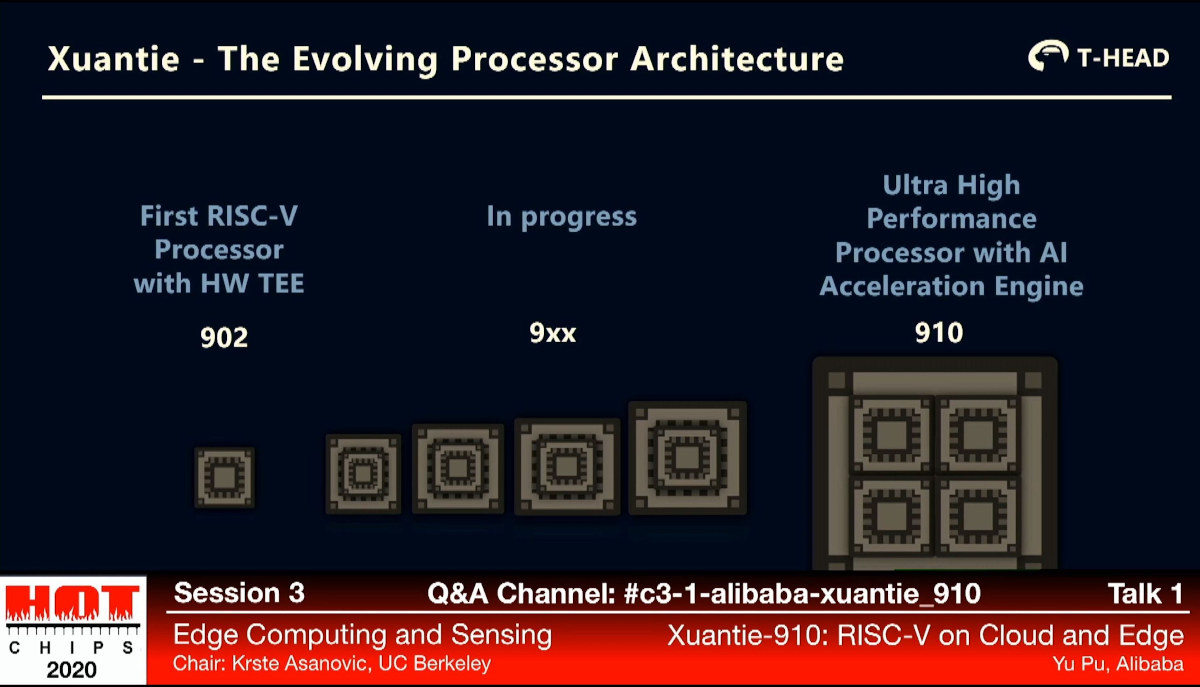

La société ne travaille pas uniqument sur des cœurs haute performance, ils ont déjà conçu le cœur de microcontrôleur XT902 (comparable au Cortex-M0+), et il existe des plans pour les cœurs XT903, XT907, XT908 afin d'élaborer une gamme complète entre le XT902 et XT910.

Commentaires récents