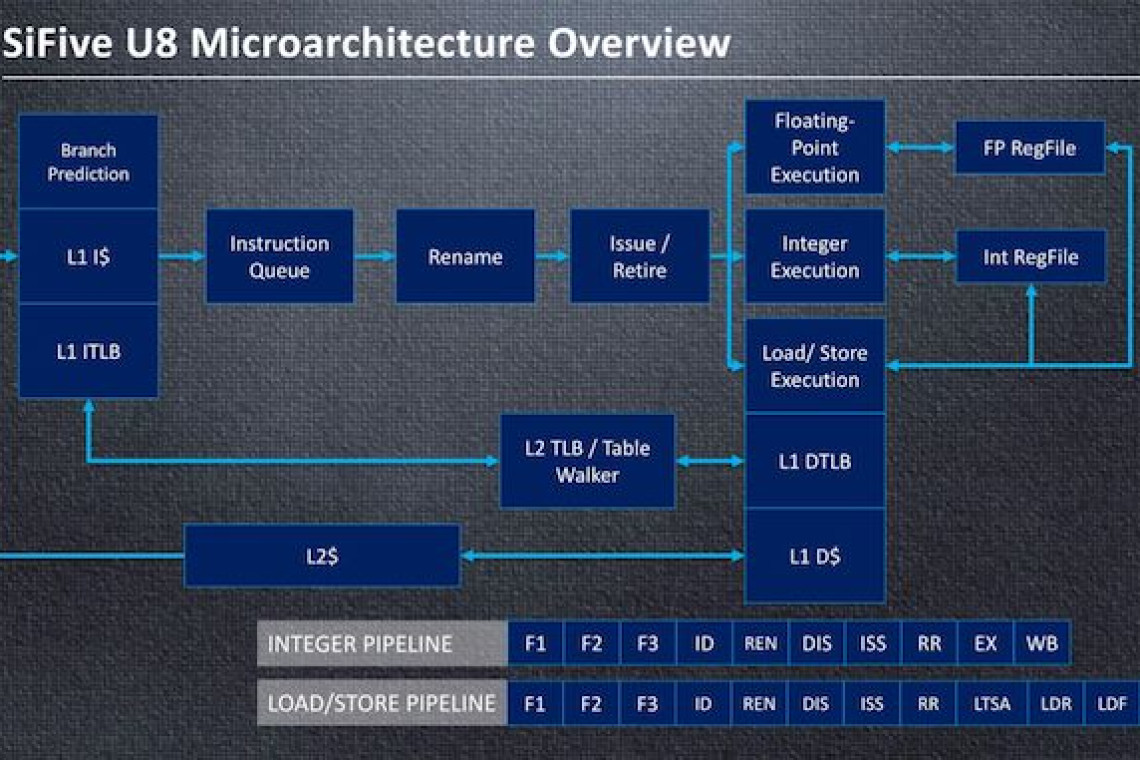

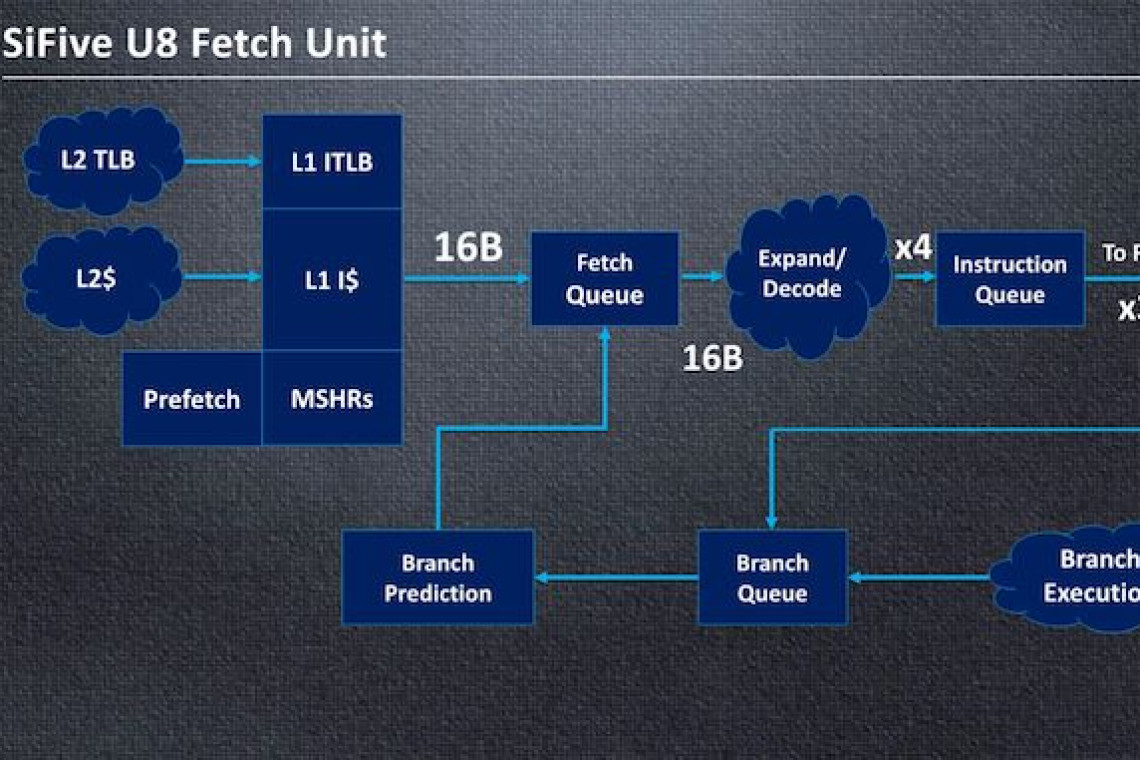

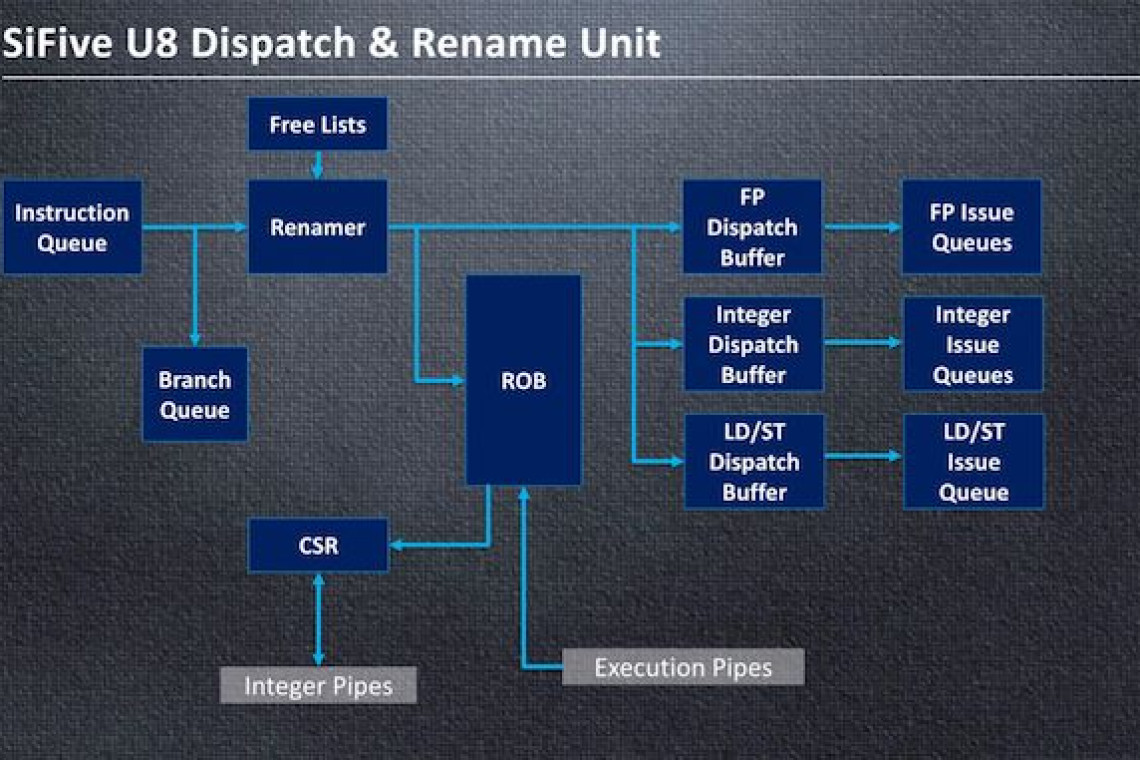

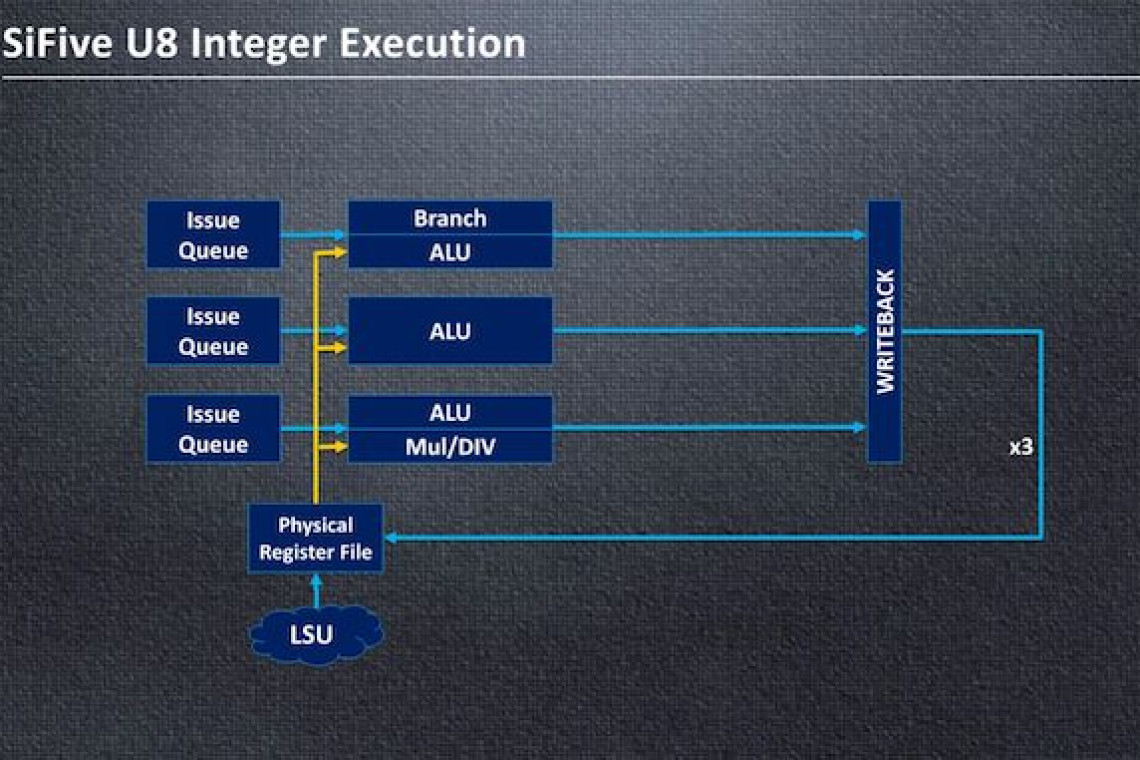

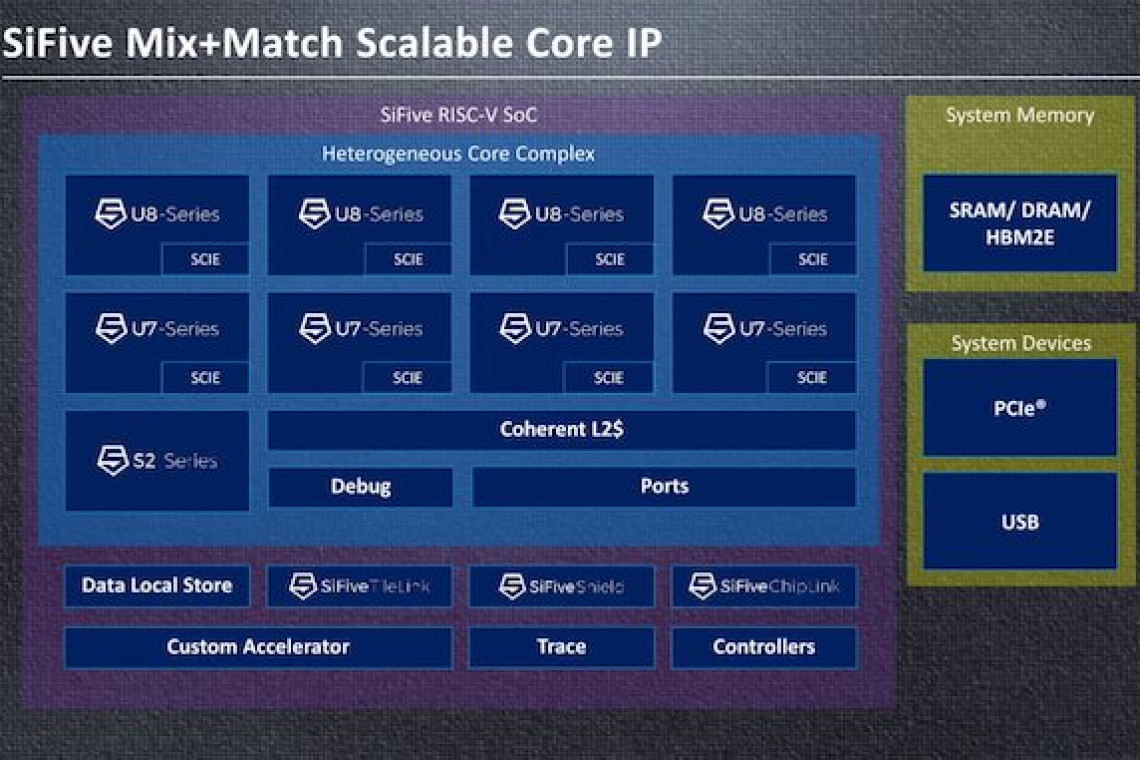

Le nouveau Core IP SiFive de la série U8 est basé sur l’ISA RISC-V. Il s’agit d’une conception superscalaire, qui propose un pipeline évolutif hors d’ordre avec des options configurables pour une utilisation en temps réel ou des processeurs d’application. Conçue pour offrir une efficacité énergétique et des surfaces exceptionnelles, la microarchitecture SiFive série U8 offre d’excellentes performances, avec la personnalisation que les clients exigent de SiFive.

La microarchitecture de la série SiFive U8 a été conçue pour offrir une amélioration de l'efficacité par zone de plus de 1,5 fois et une performance par watt de 1,5 fois par rapport au produit concurrent disponible aujourd'hui. SiFive U8-Series Core IP est compatible avec plusieurs cœurs avec une unité de gestion de la mémoire compatible avec Linux pour permettre la conception générale de processeurs d’application. La microarchitecture SiFive de la série U8 peut prendre en charge le mode temps réel pour les opérations critiques, en exploitant les fonctionnalités généralement vues auparavant uniquement sur les conceptions haut de gamme implémentées dans des nœuds de processus avancés.

Doté d'une unité à virgule flottante en option, d'une fonctionnalité d'extension d'instructions personnalisées et d'une prise en charge d'extension vectorielle RISC-V, le Core IP SiFive série U8 peut être configuré et personnalisé parfaitement au cas d'utilisation cible, que ce soit dans le ecteur Automobile ou de l'AI.

La nouvelle SiFive HBM2E + IP est conçue pour permettre les charges de travail intensives en calculs, y compris le traitement d'apprentissage en profondeur dans les dispositifs de calcul, de centre de données et d'IA de haute performance. Doté d'interfaces standard, SiFive HBM2E + IP s'intègre facilement dans de nouvelles conceptions et permet d'optimiser le chemin processeur à mémoire, en utilisant une interface évolutive permettant à la fois la conception de puces et les performances.

Validée par une technologie de processus de pointe à 7 nm, la solution SiFive HBM2E + offre une bande passante mémoire allant jusqu'à 400 Gbps, soit 3,2 Gbps par broche. Les propriétés d’empilement de HBM permettent de réduire l’empreinte au sol et de réduire la consommation d’énergie par rapport à une mémoire de type DDR à capacité similaire, avec une bande passante supérieure, essentielle au traitement des charges de travail d’apprentissage approfondi nécessitant une mémoire intense.

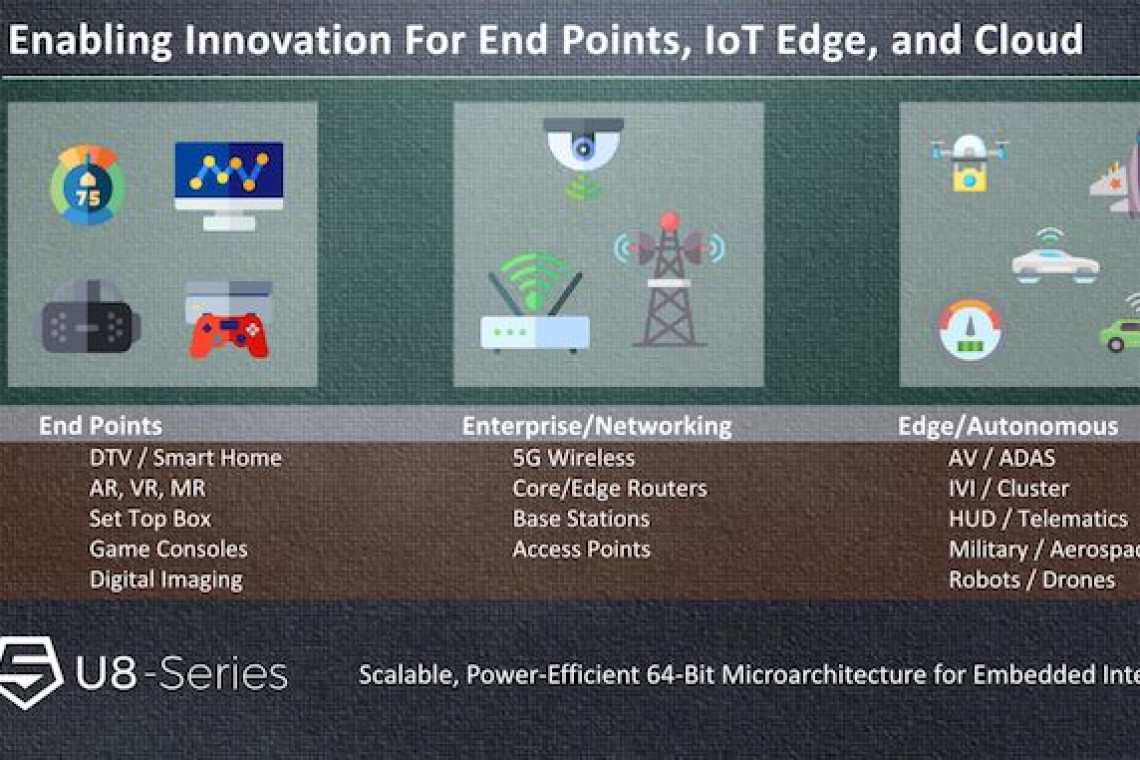

Les principaux marchés en croissance exigent un traitement plus efficace et plus rapide des données au niveau local, à mesure que le besoin d'IA à la limite et à la fin augmente rapidement. De nouvelles conceptions spécifiques à des domaines pour les accélérateurs de centres de données, les systèmes automobiles, l’IoT industriel et les appareils IoT grand public deviennent rapidement le paradigme de conception préféré, parfaitement alignées sur la méthodologie, le portefeuille et les compétences de SiFive.

L'adoption de cœurs configurables basés sur RISC-V ISA et d'interconnexions à source ouverte pour permettre au silicium hautes performances de s'assurer que les conceptions personnalisées ne sont pas fragmentées. Les extensions d'instructions personnalisées SiFive fournissent des accélérations spécifiques adaptées à la charge de travail sans impact sur la compatibilité des extensions ISA de base ou formelles et sont prises en charge par des outils standard tels que IAR Workbench.

Le nouveau cœur de processeur et les interfaces de mémoire de SiFive associent l’adresse IP nécessaire pour réussir sur les marchés à forte croissance qui nécessitent des processeurs d’application spécifiques à un domaine. Les applications automobiles, IoT Edge et End Point AI, ainsi que les concepteurs d'accélérateurs de centres de données peuvent tous bénéficier des performances évolutives et de la puissance de traitement fournies par SiFive Core IP et HBM2E +. "C’est passionnant de voir la publication de la microarchitecture hors d’ordre de la série U8 par SiFive", a déclaré Kevin Krewell, analyste principal chez TIRIAS Research. "De nouveaux cœurs à capacité Linux et plus performants permettent à SiFive d’entrer sur de nouveaux marchés et d’élargir RISC-V La combinaison d’ISA et d’interconnexions standard à source ouverte, ainsi que de normes industrielles communes et de la nouvelle technologie de mémoire à bande passante élevée, permet la personnalisation, l’adressage d’un plus grand nombre de marchés d’applications et l’amélioration du TAM de la société. »

"L'introduction de la nouvelle microarchitecture SiFive série U8 constitue une étape majeure", a déclaré Naveed Sherwani, PDG de SiFive. «La disponibilité d'un processeur RISC-V extensible hors d'usage à utiliser dans des applications spécifiques à un domaine annonce une nouvelle ère de conceptions de SoC configurables et personnalisées basées sur RISC-V. SiFive continue de dominer avec des solutions IP et silicium pour l'automobile, la connexion de centre de données et Edge AI. ”

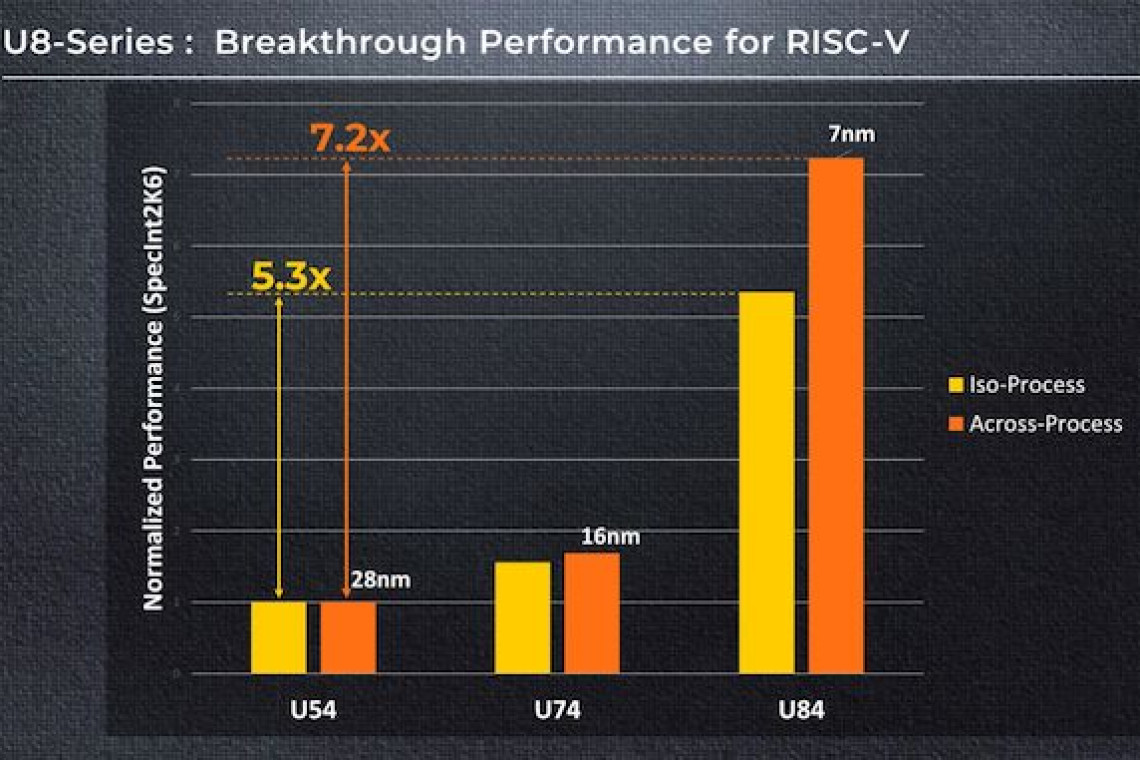

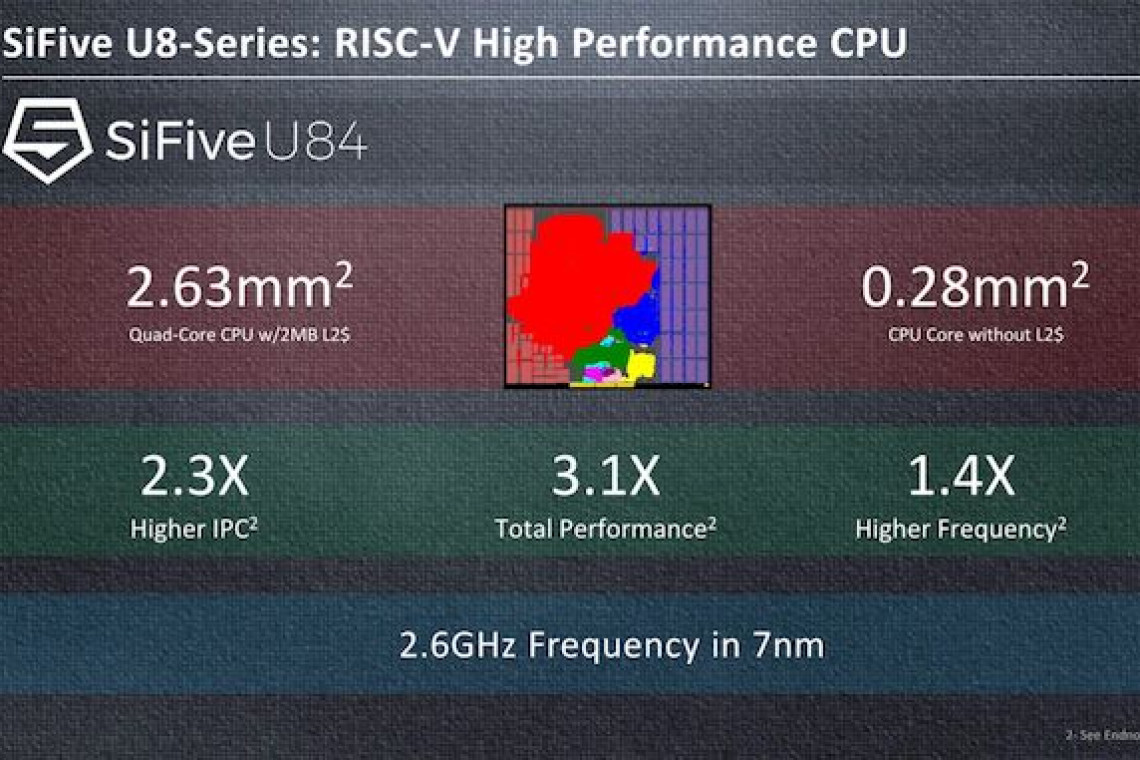

SiFive annonce ses processeurs RISC-V U84 aussi performants que des ARM Cortex A72 pour un consommation réduite de 50%